# Modularity in the Design of Robust Distributed Algorithms

THIS IS A TEMPORARY TITLE PAGE

It will be replaced for the final print by a version provided by the service academique.

Giuliano Losa giuliano.losa@epfl.ch

**EPFL**

### **Abstract**

A distributed system consists of several computers, connected by a network, that need to cooperate to accomplish a task. Distributed systems are now part of our everyday lives. From our means of transportation (cars contain dozen of computers) to our means of communication (the internet contains millions of computers), we must rely on distributed systems every day. Yet building trustworthy distributed systems is a challenge.

Distributed systems are especially hard to program because they need to constantly adapt their strategy to handle a changing environment: mobile components change location, communication links fail, servers crash and restart, users come and go, and attackers may try to break the system.

Experience has shown that it is not practical to combine several strategies ad-hoc, without strong guiding principles. The need to change strategy on the fly results in distributed algorithms that are so difficult to understand that they cannot be guaranteed to operate safely, let alone efficiently. Changing back and forth between only two different strategies is already a research challenge, but it is not sufficient given the wide variety of possible behavior of the environment. Adding more strategies quickly becomes intractable because every strategy must be able to pass the baton to every other, leading to a quadratic number of challenging cases.

This thesis proposes the Speculative Linearizability framework for building and reasoning about adaptive distributed algorithms in a practical way. The Speculative Linearizability framework soundly abstracts over the interaction between strategies, allowing each strategy to be designed, tested, and verified independently of the others. The abstraction guarantees that independently designed strategies are nevertheless compatible by construction: there is no need to check whether every strategy can pass the baton correctly to every other. By clearly separating each strategy, the Speculative Linearizability framework eliminates the complexity blowup that makes ad-hoc approaches impractical.

Our results have been been formalized in the TLA+ language and thoroughly tested with the TLC model checker. Moreover, we have proved and mechanically checked with the Isabelle/HOL interactive theorem prover that the core of our main result, the composition theorem, is correct.

**Keywords:** Distributed Computing, Adaptive Systems, Modularity, Speculation, Fault-Tolerance.

### Résumé

Un système informatique distribué est constitué des plusieurs calculateurs, communicant à travers un réseau, qui coopèrent pour mener à bien une tâche. Peut-être sans le savoir, nous dépendons tous les jours de systèmes informatiques distribués. Nos moyens de transports, voitures, avions ou trains, sont composés de dizaines voir de centaines de processeurs interconnectés. L'Internet est composé de milliers d'entités autonomes aussi bien physiquement que administrativement qui coopèrent pour nous offrir accès au web. Les "calculateurs" d'Internet, serveurs et autres routeurs, se comptent par millions.

Les systèmes distribués sont pourtant très difficiles à programmer car leur environnement est imprévisible : le système doit faire face à des pannes en tous genres, à des délais de communications, et au comportement imprévu des ses utilisateurs. Pour accomplir sa tâche efficacement dans un tel environnement, un algorithme distribué doit adapter sa stratégie aux changements de son environnement.

Les expériences passées ont montré qu'il n'est pas envisageable en pratique, sans fondations théoriques adéquates, de changer de stratégie dynamiquement lors du fonctionnement du système. Chaque stratégie doit être capable de passer le témoin à chaque autre stratégie. L'enchevêtrement qui résulte d'une telle combinaison de stratégies s'est avéré trop difficile à analyser pour en garantir le bon fonctionnement.

Cette thèse propose les fondations théoriques et une méthode, efficace en pratique, qui simplifient le développement des algorithmes distribués adaptatifs. La méthode présentée permet de développer, tester, et d'analyser chaque stratégie indépendamment des autres stratégies, tout en garantissant que les stratégies soient compatibles par construction. Il n'y a alors plus besoin de considérer l'enchaînement des stratégies. L'indépendance des stratégies les unes vis-à-vis des autres élimine la complexité du problème à sa source et permet, comme il est montré dans plusieurs exemples, d'obtenir des algorithmes adaptatifs très performants et sûrs.

Les résultats de cette thèse ont étés rigoureusement testés par Model Checking avec le logiciel TLC. De plus, le théorème à la base de nos résultats a été démontré mécaniquement avec le logiciel Isabelle/HOL.

**Mots clés :** Systèmes répartis, systèmes adaptatifs, modularité, systèmes spéculatifs, tolérance aux pannes.

## Acknowledgements

I would like to thank my advisors, Rachid Guerraoui and Viktor Kuncak, for giving me the opportunity to pursue a PhD and for their guidance towards its completion.

I thank the members of the jury, Joseph Sifakis, Tobias Nipkow, Stephan Merz, and André Schiper, for the time spent reviewing and evaluating my thesis and for helping me improve my thesis.

I thank all my colleagues and friends from EPFL for making my PhD more enjoyable. Let me cite a few, from the LPD: El Mahdi El Mhamdi, Swan Dubois, Nicolas Braud-Santoni, Mihai Letia, Victor Bushkov, Matej Pavlovic, Maxime Monod, Dan Alistarh, Florian Huc, Kristine Verhamme, Fabien Salvi; from the LARA: Eva Darulova, Hossein Hojjat, Etienne Kneuss, Philippe Suter, Ruzica Piskac, Mikael Mayer, Filip Konecny, Regis Blanc, Pierre-Emmanuel Cornilleau; from the LGG: Sofien Bouaziz, Mario Deuss, and Andrea Tagliasacchi.

Also many thanks to my friends outside EPFL: Martin and Mathias Lefort, Benjamin Provost, Yann Maillet-Contoz, the Wintsch Chalpin family, the Milani family, Nathalie Nowak, Kurt Jungbluth, Stefan Prennschütz-Schützenau, and my flatmates Julie Degand, Elsa Courdier, and Michael Ferez.

Special thanks to Gelare for her support during end of my PhD.

Finally, my biggest thanks go to my family, Bertrand, Pierre André, Roberto, Marie-Hélène, Gisèle, and Françoise and Jackie.

Lausanne, Friday 7<sup>th</sup> February, 2014

# **Contents**

| Al | ostra  | t                                                                                       | iii |

|----|--------|-----------------------------------------------------------------------------------------|-----|

| Re | ésum   | 5                                                                                       | v   |

| Ac | cknov  | vledgements                                                                             | vi  |

| Ta | ıble o | f Contents                                                                              | xi  |

| 1  | Intr   | oduction                                                                                | 1   |

|    | 1.1    | Robust Distributed Systems and Adaptation                                               | 1   |

|    | 1.2    | The Problem of Dynamically Changing Strategy                                            | 2   |

|    | 1.3    | Contributions                                                                           | 4   |

|    | 1.4    | Speculative Linearizability                                                             | 4   |

|    | 1.5    | Model Checking and Mechanically-Checked Proofs                                          | 6   |

|    | 1.6    | Publications                                                                            | 6   |

| 2  | Spe    | rifying Distributed Systems                                                             | 7   |

|    | 2.1    | Introduction                                                                            | 7   |

|    | 2.2    | Notation                                                                                | 8   |

|    | 2.3    | I/O Automata                                                                            | 8   |

|    |        | 2.3.1 Definition of I/O Automata and their Traces $\ \ldots \ \ldots \ \ldots \ \ldots$ | 10  |

|    |        | 2.3.2 Composition                                                                       | 12  |

|    |        | 2.3.3 Hiding and Projection                                                             | 14  |

|    |        | 2.3.4 Simulation Proofs                                                                 | 14  |

|    | 2.4    | TLA+                                                                                    | 15  |

|    |        | 2.4.1 A Basic Example                                                                   | 16  |

|    |        | 2.4.2 The Implementation Relation                                                       | 16  |

|    |        | 2.4.3 Refinement Mappings                                                               | 17  |

|    |        | 2.4.4 Hiding Internal State                                                             | 18  |

|    |        | 2.4.5 Composing Specifications                                                          | 18  |

|    |        | 2.4.6 Expressing I/O Automata Specifications in TLA+                                    | 19  |

|    | 25     | Conclusion                                                                              | 22  |

#### **Contents**

| 3 | Line | earizability: I/O-Automata Specification and Properties | <b>23</b> |

|---|------|---------------------------------------------------------|-----------|

|   | 3.1  | Introduction                                            | 23        |

|   | 3.2  | Data Types and Data-Type Representations                | 24        |

|   |      | 3.2.1 Data Types                                        | 24        |

|   |      | 3.2.2 Data-Type Representations                         | 24        |

|   |      | 3.2.3 Examples of Data-Type Representations             | 27        |

|   |      | 3.2.4 Space of Possible Representations                 | 30        |

|   | 3.3  | I/O-Automaton Specification of Linearizability          | 31        |

|   |      | 3.3.1 Well-Formed Data-Type Implementations             | 31        |

|   |      | 3.3.2 The Linearizability I/O Automaton                 | 33        |

|   |      | 3.3.3 Examples: consensus and test-and-set              | 34        |

|   | 3.4  | 8                                                       | 35        |

|   |      | 3.4.1 The $Lin'$ I/O Automaton                          | 36        |

|   |      | 3.4.2 The <i>NDLin</i> I/O Automaton                    | 39        |

|   | 3.5  | The Abstraction Theorem                                 | 40        |

|   | 3.6  | The Inter-Object Composition Theorem                    | 41        |

|   | 3.7  | The Original Definition of Linearizability              | 41        |

|   |      | 3.7.1 Happens-before relation                           | 41        |

|   |      | 3.7.2 Safe reordering                                   | 42        |

|   |      | 3.7.3 Closure of a trace                                | 43        |

|   |      | 3.7.4 Linearizability                                   | 43        |

|   | 3.8  | Conclusion                                              | 43        |

| 4 | Ada  | ptive Algorithms and Modular Reasoning                  | 45        |

|   | 4.1  | Introduction                                            | 45        |

|   | 4.2  | Related Work                                            | 46        |

|   | 4.3  | Modeling Adaptive Algorithms with I/O Automata          | 47        |

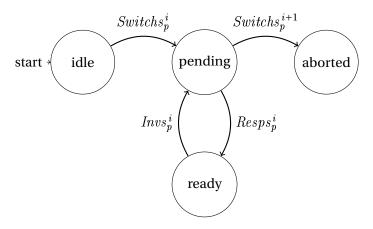

|   | 4.4  | A Model for Adaptive Algorithms                         | 48        |

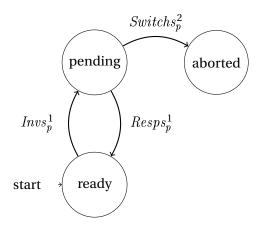

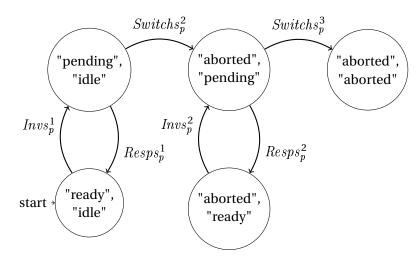

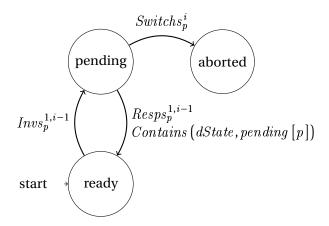

|   |      | 4.4.1 Well-Formed Mode Instances                        | 48        |

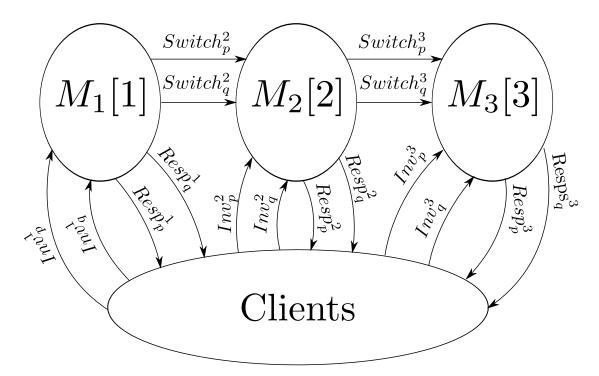

|   |      | 4.4.2 Composing Modes Instances                         | 51        |

|   |      | 4.4.3 A Correctness Condition for Adaptive Algorithms   | 53        |

|   | 4.5  | Modular Properties                                      | 54        |

|   |      | 4.5.1 The Modularity Theorem                            | 56        |

|   | 4.6  | Conclusion                                              | 58        |

| 5 | Spe  | culative Linearizability                                | 61        |

|   | 5.1  | Introduction                                            | 61        |

|   | 5.2  | Related Work                                            | 62        |

|   | 5.3  | Recoverable Data-Type Representations (RDRs)            | 63        |

|   |      | 5.3.1 The History Data-Type Representation              | 64        |

|   | 5.4  | Speculative Linearizability                             | 66        |

|   |      | 5.4.1 The I/O Automaton $SLin$ [1, $i$ ]                | 66        |

|   |      | 5.4.2 Linearizability of <i>SLin</i>                    | 69        |

| C  | ırricı | ulum Vitae                                                                     | 233       |

|----|--------|--------------------------------------------------------------------------------|-----------|

| В  | Isab   | pelle/HOL Theories                                                             | 161       |

|    | A.4    | Auxiliary Definitions                                                          | 159       |

|    | A.3    | Shared-Memory Consensus                                                        | 152       |

|    | A.2    | Message-Passing Adaptive Algorithms                                            | 133       |

|    |        | Speculative Linearizability                                                    |           |

| A  | TLA    | + Specifications                                                               | 115       |

| Bi | bliog  | raphy                                                                          | 107       |

|    |        | 8.1.4 Practical Applications of Speculative Linearizability in Shared-Memory . | 104       |

|    |        | 8.1.3 Debugging Proofs at an Intermediate Level of Granularity                 | 103       |

|    |        | 8.1.2 Debugging Byzantine Fault-Tolerant Algorithms                            | 103       |

|    |        | 8.1.1 Byzantine Faults in the Speculative Linearizability Framework            | 102       |

|    | 8.1    | Future Work                                                                    | 102       |

| 8  |        | clusion                                                                        | 101       |

| 7  |        | lying Speculative Linearizability to Shared-Memory Consensus                   | 97        |

| 7  |        |                                                                                |           |

|    | 6.5    | Conclusion                                                                     | 94        |

|    |        | 6.4.3 Progress Guarantees of $QZ$                                              | 94        |

|    |        | 6.4.2 ZLight                                                                   | 92        |

|    | 6.4    | The $QZ$ Algorithm                                                             | 89        |

|    | C 4    | 6.3.2 Behavior of The $Fast(i)$ I/O automaton                                  | 86<br>89  |

|    |        | 6.3.1 Behavior of The Safe (i) I/O automaton                                   | 83        |

|    | 6.3    | Fast and Safe Modes                                                            | 82        |

|    | 6.2    | Related Work                                                                   | 82        |

|    | 6.1    | Introduction                                                                   | 79        |

| 6  |        | lying Speculative Linearizability to Fault-Tolerant Message-Passing Systems    | <b>79</b> |

|    | 5.6    | Conclusion                                                                     | 76        |

|    | 5.5    | Proving Idempotence Mechanically                                               | 75<br>76  |

|    |        | 5.4.5 <i>SLin</i> is a modular property                                        | 74        |

|    |        | 5.4.4 Idempotence of $SLin$                                                    | 73        |

|    |        | L - 1                                                                          | 69        |

|    |        | 5.4.3 The I/O Automaton $SLin[i,j]$                                            |           |

## 1 Introduction

#### 1.1 Robust Distributed Systems and Adaptation

Complex systems on which we depend on almost every day, like cars, airplanes, the electric grid, or the internet, contain dozens, hundreds, thousands, or even millions of computers. To deliver their services, these computers need to cooperate, forming what is called a *distributed system*: a system composed of multiple computers, spatially separated, that cooperate in order to achieve a collective goal.

The components of a distributed system behave according to a *distributed algorithm*, which assigns to each component an algorithm to execute. However, some aspects of a distributed system are not controllable and cannot be specified by an algorithm. For example, smartphones change location, initiate communication, are turned on and off, etc. independently of the will of the network operator. Yet the cellular network must provide reliable service at all times. In the internet, routers and link may fail unexpectedly, users may start downloading files at any time, etc. Yet packets should be routed reliably at all times.

A distributed algorithm is usually said *correct* when it is *safe* and *live* [47], i.e., it never does anything wrong and it eventually delivers its service despite the unpredictable behavior of its components. For example, a cellular network may be said correct when users are eventually able to make a call when they request it (the system is live) and when a call never reaches the wrong number (the system is safe). The wide range of possible and uncontrollable behaviors makes the design of correct distributed algorithm especially challenging. However, correctness is not the only desirable property of a distributed algorithm. In practice, we often want a distributed system to have good performance, i.e., to deliver its service fast and not only eventually.

We say that a distributed algorithm is *robust* when the system consistently delivers good performance in all the varied conditions that it may encounter. Take the example of a road-traffic monitoring system that would use the GPS capability of smart-phones to build a real-time map of the traffic density. This system should provide timely information about

the traffic on any road, regardless of it being rush hour, during which there is a high density of slow-moving users on the roads, or it begin a Sunday, when there are fewer users which move faster. Both situations are quite different. Let us think about how the algorithm running the system may gather traffic data. During rush-hour, the system must handle a lot of data. However, since cars move slowly and are densely concentrated, the algorithm could leverage the Wifi capability of smart-phones to gather the data using a gossip protocol, in which the information is propagated and aggregated from phone to phone before being sent, at a low frequency, to a server. Thanks to the gossip protocol, the algorithm would avoid overloading a central server. On Sunday there is less data to gather but the traffic is more fluid, causing unreliability in the Wifi communication between smart-phones: two cars will often get too far apart too quickly for the communication between phones to complete. Relying on the gossip protocol in this situation would bring the system to a halt. Instead, the algorithm could adapt to the situation and have the phones directly contact a central server through the cellular network.

The example of traffic monitoring shows that a robust distributed algorithm must *adapt* its strategy to the conditions that it faces. However, in many cases, there are dozens or more of possible conditions, instead of just two as in our example, and one can often not even forecast their existence, let alone provide for them, before the system is built. Therefore, one must be able to quickly add a new strategy to the algorithm, even though the system is already deployed and serving users. In other words, it must be possible to develop a robust distributed algorithm *incrementally*.

To sum up, we say that a distributed algorithm is *robust* when the following two conditions hold:

- 1. The distributed algorithm is able to *adapt* its strategy in response to change.

- 2. The distributed algorithm can easily be extended with new strategies, allowing *incremental* development.

However, achieving these two goals is challenging, intermingling performance and correctness issues.

#### 1.2 The Problem of Dynamically Changing Strategy

There are two orthogonal aspects to adaptation: the *scheduling policy* and the *switching mechanism*. A scheduling policy determines when to change strategy and which new strategy to employ. A good switching policy would rely on accurate measurements of the execution and performance of the system and could apply control theory methods so as to maximize performance while maintaining stability, avoiding runaway oscillation of the system.

In contrast, a switching mechanism is an algorithm whose task is to bring about the changes dictated by the scheduling policy quickly and transparently to the users. The main issue faced by a switching mechanism is that changing the strategy of the whole system requires

coordinated changes in all of its components while maintaining the functionality of the system to make adaptation transparent to the users. In this thesis we will study switching mechanisms, i.e. the problem of dynamically switching strategy without interrupting the functionality of the system. This problem is well-known [83, 78, 17, 93] but, with the exception of the Abstract framework [35], we are not aware of any systematic and general framework to address it.

In order to understand the switching mechanism problem, let us examine the case of State Machine Replication (abbreviated SMR) [54, 87]. SMR is a general technique used to build robust linearizable implementations of data types [57, 37]. SMR algorithms like Paxos [47] or PBFT [14], which are not adaptive, are notoriously hard to understand. The formal correctness proof of Disk Paxos [43] is about 7000 lines long. Only an informal proof, 35 pages long, of a simplified version of PBFT is known to the authors [13].

Adaptive SMR protocols are even harder. For instance, the Zyzzyva [46] protocol combines PBFT with a fast mode implemented by a simple agreement protocol. The fast mode is more efficient than PBFT when there are no failures. In the advent of failures, the fast mode cannot make progress and Zyzzyva falls back to executing PBFT. The ad-hoc composition of the fast mode with PBFT required deep changes to both algorithms and resulted in an entanglement that is hardly understandable. Moreover, Zyzzyva, being restricted to two modes, is very fragile [88]. If the common case is not what is expected by the fast mode one falls-back to PBFT, making the optimization useless. An adversary can easily weaken the system by always making it abort the fast mode and go through the slow one. Introducing a new strategy might make the protocol more robust but would require a new ad-hoc composition, including an alternative fast mode, at a cost comparable to the effort needed to build Zyzzyva from scratch, namely a Dantean effort. Given the diversity of situations encountered in practice, we are convinced that this ad-hoc approach is simply intractable.

Now consider the general case of implementing a specification with an adaptive algorithm that can dynamically switch between n different modes. Despite changing mode, the algorithm must not violate the specification. Therefore, if each mode is built ad-hoc, there are  $O\left(n^2\right)$  different switching cases in which correctness must be preserved across two different algorithms. Moreover, suppose that a new optimization is needed after the n modes have been designed. Integrating a new mode means checking that changing from an existing mode to the new mode does not violate the specification, and vice versa. It may also be necessary to modify the existing modes to accommodate for the new one. In this situation, the interactions between any two modes may need to be reconsidered. When building algorithms with only two modes is a research challenge, such an approach is intractable.

The goal of the thesis is to simplify the development of robust distributed algorithms by proposing a theory of switching mechanisms, enabling a principled approach to the construction of adaptive algorithms.

#### 1.3 Contributions

The thesis makes the following contributions:

- 1. We formalize the problem of devising robust adaptive algorithms. Our model abstracts over the scheduling policy, clarifying the task of the switching mechanism.

- 2. We propose a concrete solution, the Speculative Linearizability framework, to the problem of devising robust adaptive algorithms. The Speculative Linearizability framework soundly abstracts over the interaction between modes, allowing each mode to be designed, tested, and verified independently of the others. The abstraction guarantees that independently designed modes are nevertheless compatible by construction: there is no need to check whether every strategy can pass the baton correctly to every other.

- 3. We apply *Speculative Linearizability* to fault-tolerant message-passing algorithms, showing that state of the art algorithms, which are notoriously intricate, can be easily optimized with our framework, and to shared-memory algorithms, showing that Speculative Linearizability has a wide applicability.

- 4. We provide supporting material for others to use Speculative Linearizability to design new adaptive algorithms. The supporting material, consisting of TLA+ [53] specifications and Isabelle/HOL [76] theories, allows one to readily debug new adaptive algorithms with the TLC model checker and to obtain trustworthy correctness proofs of new adaptive-algorithms using Isabelle/HOL.

#### 1.4 Speculative Linearizability

Speculative Linearizability is a correctness property simplifying the analysis of *speculative algorithms*. A speculative algorithm is an optimistic adaptive algorithm: a speculative mode behaves as if a particular assumption about the environment holds, achieving high performance if the assumption is true, but possibly failing otherwise. Different modes make different assumptions, thus, if a mode fails, another mode, whose assumption is speculated to hold, can take over the execution. When a mode fails, it is required to abort and switch to the next mode transparently to the users of the system. The problem of choosing the next mode so as to maximize performance is the task of the switching policy, which we do not consider in this work. In a nutshell, speculative algorithms are agile optimistic algorithms that favor failing fast and iterating rather than over-provisioning resources.

Examples of speculation include the Ethernet protocol, where processes speculatively occupy a single-user communication medium before backing off if collision is detected, or branch prediction in microprocessors, where the processor speculates that a particular branch in the code will be taken before discarding its computation if this is not the case. More recent instances of speculation include optimistic replication [46] or adaptive mutual exclusion [44]. In fact, most practical concurrent systems are speculative. In general, speculative systems may choose between a large number of modes, in order to closely match a changing environment.

In order to continue the execution after a mode failure, the two consecutive modes have to synchronize, using a switching mechanism that both mode understand. As we have seen in the example of SMR, designing algorithms which can abort and switch is very challenging. This is the problem that Speculative Linearizability addresses.

Speculative Linearizability builds on the notion of Linearizability [37, 51, 52], which already simplifies the development of distributed systems, but has no provision for adaptivity or speculation. The correctness of a system of processes communicating through linearizable objects reduces to the correctness of the sequential executions of that system. In other words, linearizability reduces the difficult problem of reasoning about concurrent data types to that of reasoning about sequential ones. In this sense, the use of linearizable objects greatly simplifies the construction of concurrent systems. At first glance, the design and implementation of linearizable objects themselves looks also simple. One can focus on each object independently, design the underlying linearizable algorithm, implement and test it, and then compose it with algorithms ensuring the linearizability of the other objects of the system. In short, linearizability is preserved by *inter-object composition*: a set of objects is linearizable if and only if each object is linearizable when considered independently of the others. However, the inter-object composition property does not help designing *robust* linearizable objects, which can switch between several modes.

Linearizable systems offer an interface composed of *invocation actions* and *response actions*. *Speculative linearizability* extends linearizability with the notion of *switch actions*, which makes it significantly richer than linearizability, yet it reduces to linearizability if these actions are ignored. Speculative linearizability augments classical linearizability with a new aspect of composition. Not only a system of concurrent objects can be considered correct if each of them is correct (*inter-object composition*), but a set of algorithms implementing different modes of the *same* object is correct if each mode is correct (*intra-object composition*). We express this new aspect through a new composition theorem. Intuitively, speculative linearizability captures the idea of *safe* and *live abortability*. A mode can abort if the assumptions behind speculation reveals wrong. When it does abort, it does so in a safe manner, by preserving the consistency (linearizability) of the object state. Moreover, the abort is also performed in a live manner, because a new mode can take over and make progress. Processes can switch asynchronously from one mode to another, without the need to wait for one another, as long as their execution, including switch actions, remains speculatively linearizable.

We apply Speculative Linearizability to the design of fault-tolerant data-type implementations in asynchronous message-passing systems. We present a speculatively-linearizable adaptive algorithm, QZ, which has the same progress guarantees as Generalized Paxos [49], a state of the art algorithm in the domain and a notoriously intricate algorithm, by combining two simple modes. Being speculatively linearizable, QZ can be composed with any other speculatively-linearizable mode to boost its performance for new conditions, whereas Generalized Paxos is not easily extensible. Like Generalized Paxos, our algorithm can execute commuting requests in one message round-trip, a practical and common case. We

also apply Speculative Linearizability to shared-memory consensus, obtaining a speculative shared-memory algorithm that uses only register if no processes contend on shared data structures. Our speculative shared-memory consensus algorithm demonstrates that Speculative Linearizability is also applicable in shared-memory.

#### 1.5 Model Checking and Mechanically-Checked Proofs

The behavior of even modest distributed algorithm is often complex and contains many details that are notoriously easy to overlook, leading to bugs in implementations and errors in proof. To avoid making mistakes, we need the support of software tools that can test whether an algorithm has its intended properties or that can check our proofs. Therefore, we have formalized most of our work in TLA+, as well as the core property of Speculative Linearizability in Isabelle/HOL. The TLC model-checker allowed us to quickly explore new algorithms and debug them, while Isabelle/HOL allowed us to write mechanically-checked proofs. All of the algorithms presented in the thesis have been exhaustively model checked for small system sizes. A variant of Speculative Linearizability, exercising the principle at the core of Speculative Linearizability, has been proved correct in Isabelle/HOL [32].

The TLA+ and Isabelle/HOL specifications are one of contributions of the thesis, as they can be used by other researchers to quickly start debugging, with the TLC model checker, and proving, with Isabelle/HOL, new speculative algorithms.

#### 1.6 Publications

Part of the work presented in this thesis has been published in the following three publications:

- Rachid Guerraoui, Viktor Kuncak, and Giuliano Losa. "Speculative Linearizability". In: PLDI. Ed. by Jan Vitek, Haibo Lin, and Frank Tip. ACM, 2012, pp. 55–66. DOI: 10.1145/ 2254064.2254072.

- Rachid GUERRAOUI, Viktor KUNCAK, and Giuliano LOSA. "Abortable Linearizable Modules". In: *The Archive of Formal Proofs*. Ed. by Gerwin KLEIN, Tobias NIPKOW, and Lawrence PAULSON. Formal proof development. http://afp.sf.net/entries/Abortable\_Linearizable\_Modules.shtml, 2012.

- Dan ALISTARH et al. "On the cost of composing shared-memory algorithms". In: SPAA.

Ed. by Guy E. BLELLOCH and Maurice HERLIHY. ACM, 2012, pp. 298–307. DOI: 10.1145/2312005.2312057

## 2 Specifying Distributed Systems

#### 2.1 Introduction

Distributed algorithms are often very complex and some details of their structure and behavior are notoriously easy to overlook. To avoid mistakes, one can writing precise specifications of an algorithm and its properties in a formal specification language. Tools such as model checkers can then be used to test whether the algorithm satisfies its properties. In general, only a subset of all the behaviors of the algorithm can be explored by model checking. However, fully automatic model checkers can be easily used as debuggers of specifications. Writing a detailed formal proof can raise our confidence in the correctness of an algorithm beyond what is possible with a model-checker. However, only when a formal proof is *mechanically checked* by a computer can we reach the assurance that a distributed algorithm is correct.

This chapter is an introduction to the basic concepts of the theory of I/O automata and of the TLA+ language. In the rest of the thesis, we use the theory of I/O automata [61] for informal discussions and the TLA+ [53] language for formal specifications. In section 5.5, we describe the formalization and mechanical proof of one of our results in the Isabelle/HOL [76] interactive theorem prover.

Distributed algorithms can be concisely represented as the composition of several I/O automata because the components of a distributed system interact by performing *discrete joint actions* and otherwise evolve completely *asynchronously*. Composing two components represented as I/O automata results exactly in a system in which the two components, which are otherwise completely asynchronous, interact through specific discrete joint actions. Therefore, I/O automata composition accurately models the interaction between components of a distributed system.

In an effort to provide a trustworthy theory of adaptive distributed systems, we have formalized our work in the TLA+ language and we have checked the correctness of our results with the TLC model checker [94]. In section 2.4.6, we describe how to translate I/O automata specifications in TLA+ in order to use the TLC model checker.

There are many other specification frameworks targeting the description of distributed systems and their properties. Some frameworks are well-known as frameworks while others are better known by the name of their main component. Let us cite the BIP framework (Behavior, Interaction, and Priority) [6], Reactive Modules [4], Promela and the SPIN model checker [40], the NuSMV model checker [18], Bigraphical Reactive Systems [70], Abstract State Machines [10], and process calculi like CSP [39], the  $\pi$ -calculus [71, 72], and Petri nets [82].

In the rest of this chapter we present the theory of I/O automata, restricted to finite traces, and the TLA+ language. We also show how to express I/O automata specifications in TLA+, with the aim of checking them with the TLC model-checker.

Apart from section 2.4.6, which explains how to express I/O automata specifications in TLA+, the material presented in this chapter is well-known.

#### 2.2 Notation

We now present the basic mathematical notions and notations that we will use throughout the thesis.

We will make use of basic mathematical expressions that should be familiar to the reader: quantified formulas, for example  $\forall x \in S : P$  or  $\exists x \in S : P$ , set comprehensions, for example  $\{x : P\}$  or  $\{x \in S : P\}$ , literal set expressions, as  $\{e_1, \ldots, e_n\}$ , and sequences, for example  $\{e_1, \ldots, e_n\}$ . The cardinality of a set S is denoted Card(S).

If  $es = \langle e_1, ..., e_n \rangle$  is a sequence and  $i \in 1..n$ , we write es[i] for  $e_i$  and Last(e) for  $e_n$ . We use  $\circ$  for sequence concatenation,  $\langle e_1, ..., e_n \rangle \circ \langle f_1, ..., f_m \rangle = \langle e_1, ..., e_n, f_1, ..., f_m \rangle$ . Appending an element e to a sequence es is denoted Append(es, e). The set of all sequences of elements of a set E is denoted Seq(E). The length of a sequence es is denoted Seq(E).

Arrays are multi-dimensional sequences. The elements at position i,j of a two-dimensional array A is denoted  $A\left[i,j\right]$ . Functions F are the more general case of sequences and arrays whose domain is not restricted to integers.

We will often talk about the states s of an automaton and about the components of s. We write aComponent(s) for the component named aComponent of the state s, and we omit the argument s entirely when it is clear from the context.

#### 2.3 I/O Automata

In this section we present the theory of I/O automata, restricted to finite executions. We use I/O automata as our main modeling framework throughout the entire thesis. Moreover, we have formalized a small part of the theory of I/O automata, restricted to finite executions, in Isabelle/HOL and we have used it to formalize some of our results. Our Isabelle/HOL theories

can be found in appendix B.

I/O automata were first introduced by Lynch and Tuttle [61] to model asynchronous distributed systems. The theory of I/O automata is also described in details in chapter 8 of Lynch's book [59] , which contains many examples. In this section we give our own version of the theory of I/O automata, with some minor differences compared to Lynch and Tuttle. For example, the I/O automata of Lynch and Tuttle must be input-enabled whereas, to simplify specifications, ours do not.

An I/O automaton can be thought of as a *state-machine* plus an *interface*. First, an I/O automaton represent a system that has a state which is updated by taking discrete labeled actions. In this respect an I/O automaton is similar to what is often called a state machine or a traditional automata. Second, I/O automata have a *signature* which describes their interface and determines how two I/O automata synchronize when they are composed. Crucially, by using appropriate signatures, certain actions can be made internal to a component, in which case they will be executed completely asynchronously from the other components, and other actions, common to multiple components, can be matched and will be executed jointly, in a common discrete action, by all the components involved.

I/O automata conveniently describe distributed systems. A distributed system is usually composed of several components which interact through discrete transactions, or joint actions, and otherwise evolve independently. Given the characteristic of I/O automata composition, it is convenient to described distributed systems as the composition of several I/O automata representing the components of the system.

I/O automata can be used to describe a distributed system but also to specify at a high level of abstraction what a system should do. In other words, I/O automata can be used both for describing implementations and specifications.

In the rest of our work we will often need to prove that an implementation I/O automaton satisfies a specification I/O automaton. This means that the set of traces denoted by the implementation is a subset of the traces of the specification. We prove implementation using *forward simulations* or *refinement mappings* in conjunction with *history variables*.

Informally, proving by refinement that and I/O automaton A implements and I/O automaton B amounts to finding, for every step of A, a corresponding step of B which has the same label. A refinement proof allows one to reason about the individual transitions of an I/O automaton and deduce a property of all its executions. Simulation proof techniques are reviewed in detail in Lynch and Vaandrager [62].

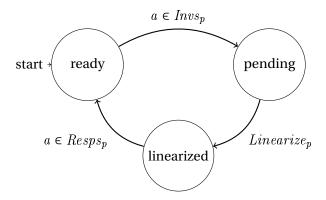

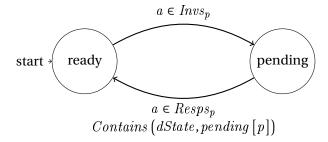

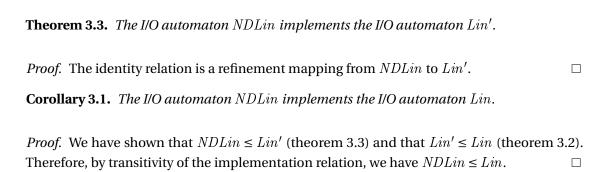

To simplify implementation proofs, one often introduces a sequence of intermediate I/O automata between the specification and the implementation and one shows using simulation proofs that, starting from the implementation, each I/O automaton implements the next in the sequence, up to the specification. For example, in section 3.4, we prove that the I/O automaton

NDLin implements the I/O automaton Lin in two steps, first showing that the I/O automaton Lin' implements the Lin I/O automaton, and then showing that NDLin implements Lin'.

Finally, there are some tools that help devise and reason about distributed algorithms described using I/O automata. First, there is the Isabelle/HOLCF formalization of I/O automata theory [75, 74], which is available in the Archive of Formal Proofs. Second, there is the IOA Toolkit [42], which is composed of a formal specification of the IOA language, a simulator [92], a verifier based on the LP theorem prover [30], and a tool for generating Java programs from IOA specifications [31]. Unfortunately, many of those tools have not been maintained and there does not seem to be an active user community at the time of writing.

We will use the theory of I/O automata throughout the whole thesis, therefore we now formally define I/O automata and their related notions such as composition and simulations. Note that we deviate from the presentation of Lynch [59] on some details.

#### 2.3.1 Definition of I/O Automata and their Traces

#### **Signatures**

A signature sig is a triple consisting of three disjoint sets of actions, Inputs (sig), the set of input actions of Sig, Outputs (sig), the set of output actions, and Internals (sig), the set of internal actions. The set of actions of a signature, denoted Acts (sig), is the union of all three components, whereas the set of external actions, denoted Ext (sig), is the union of the inputs and outputs. I/O-automata signatures are used to determine the result of composing several I/O automata, as we will see below.

#### **State machines**

A state machine  $\Sigma$  is a tuple  $\langle S, C, S_0, \delta \rangle$  where

- S is the set of states of  $\Sigma$ ;

- C is the set of actions of  $\Sigma$ ;

- S<sub>0</sub> ⊆ S is the set of initial states of Σ;

- δ is the transition relation of Σ, which is a set of transitions  $\langle s, a, s' \rangle$  where  $s, s' \in S$  and  $a \in C$ .

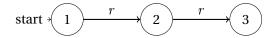

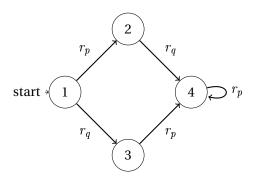

The state machine  $\Sigma$  is *deterministic* when it has a unique initial state and, for every state s and action a, there is a unique transition  $\langle s, a, s' \rangle \in \delta(\Sigma)$ . When  $\langle s, a, s' \rangle$  is a transition, we write  $s \xrightarrow{a}_{\Sigma} s'$ .

#### I/O Automata

An I/O automaton *A* consists of a signature and a *state machine*. The set of actions of the state machine must be equal to the set of actions of the signature. We now consider an I/O

automaton  $A = \langle Siq, \Sigma \rangle$ .

As shorthands, we write Inputs(A) for Inputs(Sig), Outputs(A) for Outputs(Sig), Internals(A) for Internals(Sig), Ext(A) for Ext(Sig), Acts(A) for Acts(A.sig), Start(A) for  $Start(\Sigma)$ ,  $\delta(A)$  for  $\delta(\Sigma)$ , and States(A) for  $States(\Sigma)$ .

Note that we do not require I/O automata to be input-enabled.

#### **Execution and schedules**

We now define the notions of *execution fragment, execution*, and *schedule* of a state machine. The execution fragments, schedules, and traces of an I/O automaton are simply the ones of its state machine.

The *execution fragments* of a state machine M are the sequences

$$\langle s_0, a_1, s_1, \dots, a_n, s_n \rangle \tag{2.1}$$

where, for every  $i \in 1..n$ ,  $\langle s_{i-1}, a_i, s_i \rangle$  is a transition.

The *executions* are defined as the execution fragments whose first state is an initial state,  $s_0 \in S_0$ .

We say that an action a is enabled in a state s if there exists a transition,  $\langle s, a, s' \rangle$ , whose first state if s. We say that a state is *reachable* if there exists an execution of  $\Sigma$  whose last state is s.

We define the *schedule* obtained from an execution e as the projection of e onto the actions, removing all states. The schedules of the state machine are the sequences s such that there exists an execution e whose schedule is s.

#### **Traces**

The *trace* obtained from a schedule s is the projection of s onto the external actions. The traces of A are the sequences t such that there exists a schedule s whose trace is t. We write Traces(A) for the set of traces of A. When e is an execution fragment, we define the trace of e, Trace(e), as the trace of the schedule of e. Note that the trace of e depends on the signature of the I/O automaton, whereas the schedule of e does not.

We write  $s \stackrel{t}{\Longrightarrow}_A s'$  when there exists an execution fragment e whose first state is s, whose last state is s', and such that Trace(e) = t.

#### Implementation relation

We say that an I/O automaton B implements an I/O automaton A, denoted  $B \le A$ , when A and B have the same input actions, the same output actions, and the set of traces of B is a subset of the set of traces of A.

#### 2.3.2 Composition

#### Signature composition

A set of signatures is said *compatible* when, for every two different signatures  $Sig_1$  and  $Sig_2$  in the set, the outputs of  $Sig_1$  and  $Sig_2$  are disjoint and the internal actions of  $Sig_1$  and  $Sig_2$  are disjoint.

If  $Sigs = \langle Sig_1, ..., Sig_n \rangle$  is a sequence of signatures where  $\{Sig_1, ..., Sig_n\}$  is a compatible set of signature, then the composition of Sigs,  $\prod_{i \in 1...n} Sig_i$ , is such that

– The set of inputs of  $\prod Sigs$  is the union of the set of inputs of the members of Sigs minus the union of their sets of outputs,

$$Inputs\left(\prod Sigs\right) = \bigcup_{i \in 1..n} Inputs\left(Sigs[i]\right) \setminus \bigcup_{i \in 1..n} Outputs\left(Sigs[i]\right) \tag{2.2}$$

- The set of outputs of  $\prod Sigs$  is the union of the set of outputs of the members of Sig.

$$Outputs\left(\prod Sigs\right) = \bigcup_{i \in 1...n} Outputs\left(Sigs[i]\right)$$

(2.3)

– The set of internal actions of  $\prod Sigs$  is the union of the set of internal actions of the members of Sig.

$$Internals\left(\prod Sigs\right) = \bigcup_{i \in 1..n} Internals\left(Sigs[i]\right)$$

(2.4)

#### I/O Automata composition

We say that a sequence of I/O automata is compatible when the corresponding sequence of signatures is compatible.

The composition of a sequence of I/O automata  $\langle A_1, \ldots, A_n \rangle$ ,  $\prod_{i \in 1...n} A_i$ , is defined as follows.

- The signature of the composition is the product of the signatures  $\langle Sig(A_1), ..., Sig(A_n) \rangle$ .

- The states of the composition are the sequences  $\langle s_1, ..., s_n \rangle$  where  $s_i \in States(A_i)$  for every  $i \in 1..n$ .

- The initial states of the composition are the sequences  $\langle s_1, ..., s_n \rangle$  where  $s_i$  is an initial state of  $A_i$  for every  $i \in 1..n$ .

- The transition relation of the composition is the set of transitions

$$\langle \langle s_1, \dots, s_n \rangle, a, \langle s_1', \dots, s_n' \rangle \rangle$$

(2.5)

where if a is an action of  $A_i$ , then  $\langle s_i, a, s_i' \rangle$  is a transition of  $A_i$ , else  $s_i' = s_i$ . We see that actions which belong to several components must be taken by all those components at once. Other actions are taken by their respective component while the other components remain unchanged.

Note that the traces of the composition of a compatible sequence only depends on the content of the sequence and not on the ordering of the I/O automata in the sequence. If As and Bs are two sequences of compatible I/O automata whose members are the same except for their ordering, then  $\prod As$  and  $\prod Bs$  have the same set of traces. Therefore, we will often talk about the composition of a set of I/O automata when we mean the composition of a sequences which contains exactly all the members of the set. Moreover, we write  $A \times B$  for  $\prod \langle A, B \rangle$ .

We can also refactor nested composition of I/O automata.

**Lemma 2.1.** Consider a two-dimensional array of I/O automata Ass[i,j] where  $i \in 1..n$  and  $j \in 1..m$ . Suppose that the members of Ass are pairwise compatible, i.e., for every  $i,j \in 1..n$  and  $k,l \in 1..m$  where  $i \neq j$  or  $k \neq l$ ,  $A_{i,k}$  and  $A_{j,l}$  are compatible. Then, as far as traces are concerned, composing all the I/O automata of Ass along the rows first is the same as composing along the columns first,

$$Traces\left(\prod_{i \in 1..n} \left(\prod_{j \in 1..m} A_{i,j}\right)\right) = Traces\left(\prod_{j \in 1..m} \left(\prod_{i \in 1..n} A_{i,j}\right)\right)$$

(2.6)

#### Monotonicity of composition

We can now state the first reduction theorem, which says that composition is monotonic with respect to the implementation relation: if  $A_1 \le B_1$  and  $A_2 \le B_2$  then  $A_1 \times A_2 \le B_1 \times B_2$ .

**Theorem 2.1** (Monotonicity of Composition). *If*  $\langle A_1, ..., A_n \rangle$  *and*  $\langle B_1, ..., B_n \rangle$  *are two compatible sequences of I/O automata and, for every*  $i \in 1..n$ ,  $A_i \leq B_i$ , then

$$\prod \langle A_1, \dots, A_n \rangle \le \prod \langle B_1, \dots, B_n \rangle. \tag{2.7}$$

This reduction theorem allows to reason about each component of a sequence independently and draw a conclusion about the composition of all the components.

#### 2.3.3 Hiding and Projection

The  $Hide\ (A,Acts)$  operators modifies the signature of the I/O automaton A by removing all the actions of Acts from the external signature of A and transferring them to the internal actions of A. If Sig is a signature, define

$$Hide(Sig, Acts) = \langle Inputs(Sig) \setminus Acts, Outputs(Sig) \setminus Acts, Internals(Sig) \cup Acts \rangle$$

(2.8)

Then we define Hide(A, Acts) as the I/O automaton A except that the signature of Hide(A, Acts) is Hide(Sig(A), Acts).

**Theorem 2.2.** If  $A \leq B$ , then hide  $(A, S) \leq hide(B, S)$

The projection operator proj(A, S) is defined in terms of hiding as

$$proj(A, S) = hide(A, Acts(A) \setminus S)$$

(2.9)

**Theorem 2.3.** If  $A \leq B$ , then  $proj(A, S) \leq proj(B, S)$

#### 2.3.4 Simulation Proofs

In this section we show how to prove that an I/O automaton A implements an I/O automaton B by using a refinement mapping in conjunction with history variables or by using a forward simulation. There are other types of simulation proofs, using prophecy variables or backward simulations. However we only use history variables and forward simulations in this thesis. For a thorough explanation of simulation proofs methods, we refer the reader to Lynch and Vaandrager [62].

We say that the I/O automaton  $A_H$  is obtained by adding a history variable to the I/O automaton  $A = \langle Sig, \langle S, S_0, C, \delta \rangle \rangle$  when there exist two nonempty sets H and  $H_0 \subseteq H$  such that

$$A_H = \langle Sig, \langle S \times H, S_0 \times H_0, C, \delta_H \rangle \rangle \tag{2.10}$$

where  $\delta_H$  is such that

- 1. if  $\langle \langle s, h \rangle, a, \langle s', h' \rangle \rangle$  is a transition of  $\delta_H$ , then  $\langle s, a, s' \rangle$  is a transition of  $\delta$ ;

- 2. if  $\langle s, a, s' \rangle$  is a transition of  $\delta$ , then, for every  $h \in H$ , there exists  $h' \in H$  such that  $\langle \langle s, h \rangle, a, \langle s', h' \rangle \rangle$  is a transition of  $\delta_H$ .

**Theorem 2.4.** If the I/O automaton  $A_H$  is obtained from A by adding a history variable then  $Traces(A_H) = Traces(A)$ .

A refinement mapping from A to B is a *function* f mapping states of A to states of B such that:

```

- if s \in Start(A) then f[s] \in Start(B);

- if s is a reachable state of A and s \xrightarrow{a}_{A} s', then

- if a \in Ext(B), then f[s] \xrightarrow{\langle a \rangle}_{B} f[s'];

- if a \notin Ext(B), then f[s] \xrightarrow{\Diamond}_{B} f[s'].

```

**Theorem 2.5.** Consider two I/O automata A and B which have the same external signature. If f is a refinement mapping from A to B, then A implements B.

**Corollary 2.1.** If the I/O automaton  $A_H$  is obtained from A by adding a history variable and there exists a refinement mapping f from  $A_H$  to B, then A implements B.

A forward simulation from A to B is a *relation r* relating states of A to states of B such that:

- if  $s \in Start(A)$  then  $r[s] \cap Start(B) \neq \emptyset$ ;

- if s is a reachable state of A,  $s \xrightarrow{a}_A s'$ , and  $t \in r[s]$ , then there exists a state  $t' \in r[s']$  such that

- if  $a \in Ext(B)$ , then  $t \stackrel{\langle a \rangle}{\Longrightarrow}_B t'$ ;

if  $a \notin Ext(B)$ , then  $t \stackrel{\langle}{\Longrightarrow}_B t'$ .

**Theorem 2.6.** Consider two I/O automata A and B which have the same external signature. If r is a forward simulation from A to B, then A implements B.

Forward simulations have the same power as the combination of a history variable and refinement mapping: one can prove that A implements B using a forward simulation if and only if one can prove it using a refinement mapping in conjunction with a history variable. A proof of this result appears in [62]. However, in practice, a proof may be easier with one or the other method. We will use theorem 2.6 and corollary 2.1 throughout the thesis to prove implementation relations between I/O automata. Backward simulations, not presented here, are formalized in the Isabelle/HOL theory called "Simulations" which can be found in appendix B.

#### 2.4 TLA+

In this section we introduce TLA+ informally and we show how to translate I/O automata specifications in TLA+. Although we use the theory of I/O automata in the rest of the thesis, we have translated most of our specifications in TLA+ and we have used the TLC model checker to gain confidence in their correctness. Moreover, formal versions of the specifications found in the thesis are only given in TLA+, in appendix A.

There are already very good descriptions of TLA+, see for example the book Specifying Systems [53] or [69], and we would be unable to better explain TLA+. Therefore, instead of explaining TLA+ in details, we will only highlight its main features and give a few examples that we hope will suffice for the reader to understand our discussion. Note that the TLA+ examples are typeset with the TLA+ typesetter and do not follow the notation introduced earlier.

We have used TLC within the TLA Toolbox, which offers a user-friendly Integrated Development Environment for TLA+ specifications. The TLA Toolbox provides a graphical interface to edit, check, and prove specifications correct and the TLC model checker is integrated in the toolbox and allows fast and visual debugging of specifications. All the parameters of TLC can be control with the GUI and the graphical trace explorer simplifies the analysis of error traces. TLA+ specifications can be also be proved correct and mechanically checked in the TLA Toolbox with TLAPS [21]. However TLAPS is still in development at the time of writing and we have preferred using Isabelle/HOL for writing mechanically-checked proofs.

#### 2.4.1 A Basic Example

TLA+ is a logic in which formulas denote sequences of states, called *behaviors*, in which each state is a function mapping *every* possible variable name (i.e. a string) to a value. A specification is just a formula.

Consider the following specification *Spec* 1, where x is a variable:

```

Next1 \triangleq x' = x + 1 Init1 \triangleq x = 0 Spec1 \triangleq Init1 \land \Box Next1

```

Given a state s, we say that s ["x"] is the valuation of the variable x in s. We say that s is an *initial state* of Spec1 when s satisfies Init1. We say that  $\langle s,s'\rangle$  is a step or transition of Spec1 when the states s and s' satisfy Next1. Note that Init1 has no primed variable and that the second conjunct of Spec1 is of the form  $\Box F$ , where  $\Box$  is the "always" operator of linear temporal logic and F contains primed and unprimed versions of the variable x.

The formula *Spec*1 denotes the set of all the behaviors where

- the valuation of x in the *initial state* is equal to 0, as described by *Init*1;

- for every step  $\langle s, s' \rangle$ , s'["x"] = s["x"] + 1 and all other variables *change arbitrarily*, as described by Next1. For example we could have s["z"] = 42 and s'["z"] = "hello".

The formula  $Spec\,1$  could specify a simple counter whose count is represented by the variable x .

#### 2.4.2 The Implementation Relation

Consider the following specification Spec 2.

Init2

$$\triangleq x = 0 \land y = \text{True}$$

$$Next2 \triangleq \land y' = \neg y$$

$$\land \text{if } y \text{ then } x' = x + 1 \text{ else } x' = x$$

$$Spec2 \triangleq Init2 \land \Box Next2$$

The formula Spec2 also specifies behaviors where x is repeatedly increased by one. However, between two increments of x, there is one step in which only y changes. Therefore, a behavior satisfying Spec2 does not satisfy Spec1. This is a problem because Spec1 and Spec2 could be descriptions of the same system, but at different levels of abstraction. In this case we would like to have a way of saying that Spec2 implement Spec1. As we have observed, one cannot define implementation as inclusion of the set of behaviours.

To define implementation in terms of trace inclusion we need to allow the specification Spec1 to "stutter", i.e., take steps where x does not change while the other variables are updated arbitrarily. To obtain stuttering-invariant specifications in TLA+, one must write specifications in the form  $Init \wedge \square [Next]_{vars}$ , where Init constrains the initial state,  $vars = \langle v_1, \ldots, v_n \rangle$  is the list of all the variables appearing in the Init or Next formulas, and  $[Next]_{vars}$  is defined as  $Next \vee (v'_1 = v_1 \wedge \cdots \wedge v'_n = v_n)$ .

Now reconsider our two examples, written in the form  $Init \land \Box [Next]_{vars}$ :

$$Init1 \triangleq x = 0$$

$$Next1 \triangleq x' = x + 1$$

$$Spec1 \triangleq Init1 \land \Box [Next1]_{\langle x \rangle}$$

$$Init2 \triangleq x = 0 \land y = \text{True}$$

$$Next2 \triangleq \land y' = \neg y$$

$$\land \text{If } y \text{ Then } x' = x + 1 \text{ else } x' = x$$

$$Spec2 \triangleq Init2 \land \Box [Next2]_{\langle x,y \rangle}$$

In the new versions of Spec1 and Spec2, the behaviors satisfying Spec2 also satisfy Spec1. In TLA+, we can write this fact as the implication  $Spec2 \Rightarrow Spec1$ . Thus we can equivalently define the implementation relation as inclusion of behaviors, at the semantic level, or as implication, in the logic.

#### 2.4.3 Refinement Mappings

We can prove that the specification Spec2 implements the specification Spec1 as follows. First, we prove that in all behaviors of Spec2, x is a natural number and y is a boolean. In TLA+, we state those properties as follows:

$$Inv2 \stackrel{\triangle}{=} x \in Nat \land y \in BOOLEAN$$

THEOREM  $Spec2 \Longrightarrow \Box Inv2$

The formula Inv2 is called an invariant of the specification Spec2. The proof of the theorem is done by proving that the initial states of the specification satisfy the invariant and that if the invariant holds and one step is taken then the invariant holds again. In TLA+, we state it as follows, where priming a formula is like priming all its variables:

```

LEMMA Init2 \Longrightarrow Inv2

LEMMA Inv2 \land Next2 \Longrightarrow Inv2'

```

Second, we prove that the initial states of Spec2 are initial states of Spec1 and that if the invariant Inv2 holds of the first state of a step of Spec2, then this step is also a step of Spec1. This is called a *refinement proof*. In TLA+, it is formalized as follows.

```

THEOREM Init2 \Longrightarrow Init1

THEOREM Inv2 \land [Next2]_{\langle x,y \rangle} \Longrightarrow [Next1]_{\langle x \rangle}

```

The two theorems above imply that  $Spec2 \Rightarrow Spec1$ .

#### 2.4.4 Hiding Internal State

Observe that if we look only at the x variable, Spec2 and Spec1 have exactly the same behaviors. To make the observation formal we can hide the y variable of Spec2, which we consider internal, using temporal quantification.

The specification Spec2 becomes

```

Spec2 \triangleq \exists y : Init2 \land \Box [Next2]_{\langle x,y \rangle}

```

Roughly speaking, the meaning of Spec2 is the set of all behaviors b in which the valuation of y of each state can be modified, obtaining b', in order for b' to satisfy  $Init2 \land \Box [Next2]_{\langle x,y\rangle}$ . This definition is not exactly the right one because one must take care that Spec2 remains stuttering-invariant.

We now have  $Spec2 \Rightarrow Spec1$ , as before, but also  $Spec1 \Rightarrow Spec2$ , formalizing the fact that Spec1 and Spec2 describe exactly the same behaviors when y is hidden. Without hiding y,  $Spec1 \Rightarrow Spec2$  does not hold because y is unconstrained in Spec1.

#### 2.4.5 Composing Specifications

Consider two specifications F1 and F2 of the form  $F1 = Init1 \land \Box [Next1]_{vars1}$  and  $F2 = Init2 \land \Box [Next2]_{vars2}$ , where vars1 is the set of all the variables appearing in F1 and vars2 is the set of all the variables appearing in F2. The formula  $F1 \land F2$  describes behaviors which satisfy both F1 and F2.

Suppose that vars1 and vars2 are disjoint. In this case the behaviors satisfying  $F1 \wedge F2$  are composed of four kinds of steps: steps satisfying  $Next1 \wedge Next2$ , called *joint steps*, steps satisfying  $Next1 \wedge vars2' = vars2$ , steps satisfying  $Next2 \wedge vars1' = vars1$ , and steps satisfying  $vars1' = vars1 \wedge vars2' = vars2$ .

If vars1 and vars2 intersect, then every step modifying a variable of  $vars1 \cap vars2$  must be a joint step. The specification of two communicating systems can therefore be obtained by conjoining two specifications that change common variables representing the interface between the two specifications. Note that, in the resulting specification, the two communicating components may take joint steps even when they do not communicate (when both only update variables not in  $vars1 \cap vars2$ ). In contrast, two I/O automata in a composite I/O automaton take joint steps only when communicating.

This concludes our brief presentation of TLA+. We have not addressed many important topics, like using history and prophecy variables in refinement proofs, proving temporal properties, etc.. We refer the reader to [53, 69].

#### 2.4.6 Expressing I/O Automata Specifications in TLA+

The TLC model checker allows to quickly debug specifications written in TLA+. Since we are primarily working with I/O automata, we needed to translate I/O automata specifications to TLA+ if we are to use the TLC model checker. Given an I/O automata specification, we would like to produce a TLA+ specification such that the sequences of states that satisfy the TLA+ specification are as similar as possible to the executions of the I/O automaton. In particular, we would like that an individual steps  $\langle s, s' \rangle$  of a sequence of states satisfying the TLA+ specification map unambiguously to a state transition  $\langle s_1, a, s_2 \rangle$  of the I/O automaton.

In this section we sketch a method for translating I/O automata specifications in TLA+. We have not followed this method strictly when producing the TLA+ counterparts to the I/O automata specification described in later sections, however the method exemplifies the basic ideas.

We have mainly used TLC to check that an I/O automaton A implements a I/O automaton B. To do so, we must specify both A and B in TLA+, as formulas denoted A and B and B, making sure that the transformation is sound, i.e., that A and A implements the I/O automaton A implements the I/O automaton A. We assume that A and A have the same external signature; otherwise we already know that  $A \le B$  does not hold.

For simplicity, we assume that the components of the I/O automata that we consider, i.e., actions, states, initial states, and transition relation are expressed using the constant operators of TLA+, i.e., in a subset of TLA+ that excludes all temporal operators. Hence we assume that  $||Sig(A)|| = Sig(A), ||Ext(Sig(A))|| = Ext(Sig(A)), ||Internals(Sig(A))|| = Internals(Sig(A)), ||States(A)|| = States(A), ||Start(A)|| = Start(A), and ||\delta(A)|| = \delta(A)$  are given.

The TLA+ specification  $[\![A]\!]$  uses three variables  $s_A$ , ext, and  $int_A$ . The variable  $s_A$  represents the state of A, the variable

$$ext \in [flag: BOOLEAN, act: [Ext(Sig(A))]]$$

(2.11)

is used to represent emitting an external action, and the variable

$$int_A \in [flag: BOOLEAN, act: [Internals(Sig(A))]]$$

(2.12)

is used to represent emitting an internal action. Similarly, the specification  $\llbracket B \rrbracket$  uses the variables  $s_B$ , ext, and  $int_B$ , where ext is shared with  $\llbracket A \rrbracket$ .

We use the operator

$$Emit(A, a) \triangleq$$

$$\text{IF } a \in [\![Ext(Sig(A))]\!]$$

$$\text{THEN } ext' = [flag \mapsto \neg ext.flag, act \mapsto a] \land int'_A = int_A$$

$$\text{ELSE } int'_A = [flag \mapsto \neg int_A.flag, act \mapsto a] \land ext' = ext$$

$$(2.13)$$

to update the variables ext and  $int_A$ , representing the I/O automaton A emitting the action a. We use the flag to distinguish between stuttering and emitting the same action twice.

Finally, we define

$$[A] \triangleq \wedge s_a \in [Start(A)]$$

$$\wedge \Box \left[ \exists a \in Acts(A) : Emit(A, a) \wedge \langle s_A, a, s_A' \rangle \in [\delta(A)] \right]_{\langle s_A, ext, int_A \rangle}$$

$$(2.14)$$

and, similarly, we define

$$[\![B]\!] \triangleq \wedge s_a \in [\![Start(B)]\!]$$

$$\wedge \square [\exists a \in Acts(B) : Emit(B, a) \wedge \langle s_B, a, s_B' \rangle \in [\![\delta(B)]\!]_{\langle s_B, ext, int_B \rangle}$$

$$(2.15)$$

We conjecture that the statement  $A \le B$ , in the theory of I/O automata, is equivalent to the following statement in TLA+:

$$(\exists s_A, int_A : \llbracket A \rrbracket) \Rightarrow (\exists s_B, int_B : \llbracket B \rrbracket)$$

$$(2.16)$$

Note how the state and internal actions of A and B are hidden, leaving only the variable ext, whose updates represent emitting external actions.

The transformation is simple but it is does not work well for I/O automata obtained as the composition of other I/O automata: we would like to define  $[A \times B]$  in terms of [A] and [B], for example as  $[A] \wedge [B]$ . However, taking  $[A \times B] = [A] \wedge [B]$  does not work: updates to the ext variable have to be identical in both components or no update to ext may happen,

blocking all the actions  $a \in (Ext(A) \cup Ext(B)) \setminus (Ext(B) \cap Ext(A))$ .

To allow unilateral external actions, we separate the ext variable in two variables common and  $ext_A$  in [A] and we separate the ext variable in two variables common and  $ext_B$  in [B].

The three new variables allow A or B to take a step unilaterally, which represents emitting an internal action or an external action that is not common to both A and B, or to take a joint step, which represent emitting an action common to A and B.

When translating A, separating the variable ext in the two variables common and  $ext_A$  requires knowing that A will be composed with B. Therefore, we define the translation of the transition relation of A in the context B, denoted  $Next(A)_B$ , as follows.

The formula  $Next(A)_B$  uses the variables  $ext_A$ , common,  $int_A$ , and  $s_A$ . Define

$$Emit(A, a) \triangleq$$

$$\text{IF } a \in \llbracket Ext(A) \rrbracket$$

$$\text{THEN } \wedge int'_A = int_A$$

$$\wedge \text{ IF } a \in Ext(A) \cap Ext(B)$$

$$\text{THEN } common' = [flag \mapsto \neg common.flag, act \mapsto a] \wedge ext'_A = ext_A$$

$$\text{ELSE } ext'_A = [flag \mapsto \neg ext_A.flag, act \mapsto a] \wedge common' = common$$

$$\text{ELSE } int'_A = [flag \mapsto \neg int_A.flag, act \mapsto a] \wedge \text{UNCHANGED} \langle common, ext_A \rangle.$$

The operator Emit(A, a) is used to update the variables  $ext_A$ , whose updates represent emitting an external action that is not common to A and B, and the variable common, whose updates represent emitting an external action common to A and B, and int, whose updates represent emitting internal actions of A.

Finally, define

$$Next(A)_{B} \triangleq \exists a \in Acts(A):$$

$$\land Emit(A, a)$$

$$\land a \notin Ext(B) \Rightarrow UNCHANGED(s_{B}, int_{B}, ext_{B})$$

$$\land \langle s_{A}, a, s_{A}' \rangle \in \llbracket \delta(A) \rrbracket$$

$$Next(B)_{A} \triangleq \exists a \in Acts(B):$$

$$\land Emit(B, a)$$

$$\land a \notin Ext(A) \Rightarrow UNCHANGED(s_{A}, int_{A}, ext_{A})$$

$$\land \langle s_{B}, a, s_{B}' \rangle \in \llbracket \delta(B) \rrbracket$$

$$vars \triangleq \langle s_{A}, int_{A}, ext_{A}, s_{B}, int_{B}, ext_{B}, common \rangle$$

$$\llbracket A \times B \rrbracket \triangleq$$

$$\land s_{A} \in \llbracket Start(A) \rrbracket \land s_{B} \in \llbracket Start(B) \rrbracket$$

$$\land \Box \llbracket Next(A)_{B} \land Next(B)_{A} \rrbracket_{vars}$$

$$(2.18)$$

$$(2.18)$$

$$\land Emit(B, a)$$

$$\land Emit(B$$

Note that we made sure that A and B cannot take a joint step except when they emit a common action.

If one want to check that  $A \times B \leq C$ , then the external variables of C needs to be split so as to match  $ext_A$ ,  $ext_B$ , and common.

Our method for translating composite I/O automata could be generalized to an arbitrary sequence of I/O automata but, as for the case of  $A \times B$ , the translation of each member of the sequence would depend on the signature of the other members of the sequence.

#### 2.5 Conclusion

In this chapter we have presented the theory of I/O automata and the TLA+ language.

We have seen that I/O automata can describe distributed systems concisely thanks to a notion of composition which closely matches the behavior of distributed systems. Therefore we use I/O automaton in our informal discussion throughout the thesis.

In appendix A, we also precisely specify our results in the TLA+ language. The TLA+ specifications have been thoroughly model checked with the TLC model checker. The TLA+ specifications were obtained by translating our I/O automata specifications as described in section 2.4.6.

# 3 Linearizability: I/O-Automata Specification and Properties

#### 3.1 Introduction

In this chapter we define the Lin I/O automaton, which specifies linearizability to a data type. To ease later refinement proofs, we refine the Lin I/O automaton to obtain the NDLin I/O automaton. We also present the two well-known reduction theorems that simplify the development of linearizable distributed systems, and, finally, we relate our definition of linearizability to the original definition of Herlihy and Wing [37].

We define a model in which a set of *clients*, each a separate asynchronous process, access a data type D by calling a *local* interface: the interface of the data type is available locally at each client. Linearizability specifies the allowed behaviors of the implementation of the client's interfaces. Our I/O automaton specification can be seen as a reference implementation. However, how the interface is actually implemented is of no concern in this chapter.

Central to our I/O automaton definition of linearizability is the concept of *data-type representation*. A data-type representation is a state machine whose executions specify the sequential behavior of the data type. Crucially, the transition relation of a data-type representation can be minimized by grouping states that are in a certain equivalence relation. This property will be usefull in chapter 6 to optimize the execution of commuting requests in message-passing algorithms.

To ease future refinement proofs, we also present a more nondeterministic version of the I/O automaton specification of linearizability. The refinement will also showcase the use of the *idempotence* property of data-type representations.

The first reduction theorem is the *abstraction theorem* (theorem 3.4). It allows one to soundly abstract key parts of a distributed system from their inherent concurrent behavior, instead considering them sequential. This idea is formalized in the work of Filipolic et al. [28], which explains how and why a linearizable system is *observationally equivalent* to a simpler, sequential counterpart. We propose another version of the theorem, adapted to our setting, in

section 3.5.

The second reduction theorem is the *inter-object composition theorem* (theorem 3.5). In contrast to the abstraction theorem, it concerns not the developers of a system who wish to use a linearizable component, but it concerns the designers of linearizable components. The inter-object composition theorem states that if a component  $C_1$  is linearizable to a data type  $D_1$  and a component  $C_2$  is linearizable to a data type  $D_2$ , then the parallel composition of  $C_1$  and  $C_2$  is linearizable with respect to the parallel composition of  $D_1$  and  $D_2$ . Therefore, one can reduce devising a linearizable implementation of a complex data type to devising several linearizable implementations of simpler data types.

We refer the readers to the works of Lamport [52], Herlihy and Wing [37], and Filipovic et al. [28] for more detailed discussions about linearizability and its properties. However, note that these works all rely on the traditional, trace-based, definition of linearizability, whereas our specification is an I/O automaton. The trace-based definition is presented in section 3.7.

#### 3.2 Data Types and Data-Type Representations

#### 3.2.1 Data Types

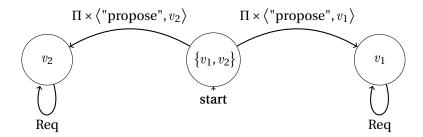

A data type describes the behavior of a system in which a set  $\Pi$  of clients invoke commands *sequentially*, i.e., a client invokes a command and receives a response before any other client can invoke a new command.

A data type D consists of a triple  $\langle C, O, \beta \rangle$ , where C is the set of *commands* of the data type, where O is the set of *outputs*, and where  $\beta$  is the set of behaviors of the data type.

Let  $Req = \Pi \times C$  be the set of *requests*. A behavior is a sequence of *operations*, where an operation is a pair  $\langle r, o \rangle$  consisting of a *request* r and of an *output* o. Note that our definition of a data type is slightly unusual because the requests contain a client identifier upon which the behavior of the data type may depend.

In the next subsection we define data-type representations. In the rest of the thesis we consider only data types which have a *deterministic*, *input-enabled*, and *idempotent* data-type representation. Unless otherwise noted, we consider such a data type  $D = \langle C, O, \beta \rangle$ .

#### 3.2.2 Data-Type Representations

A data type may be represented by means of a state machine whose schedules specify the behaviors of the data type (see section 2.3.1 for the definition of state machines). Based on this observation, we now define the notion of *data-type representation*.

A data-type representation  $\Delta$  of D is a triple  $\Delta = \langle \Sigma, O, \gamma \rangle$  consisting of a state machine  $\Sigma = \langle S, C, S_0, \delta \rangle$ , of the set of outputs O, and of an *output function*  $\gamma$ , which maps a state and

a request to an output. The members of S are called  $\Delta$ -states.

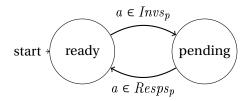

We say that a data-type representation is *deterministic* when the state machine  $\Sigma$  is deterministic.